Ver II: Credit Based Flow Control

After the first chip was out, we decided that its time to improve the router and there were two major drawbacks in this version that we targeted:

- The handshaking flow-control was performing very poorly (basically the network was working at a third of its capacity)

- The switch arbiters could not provide support for adaptive routing

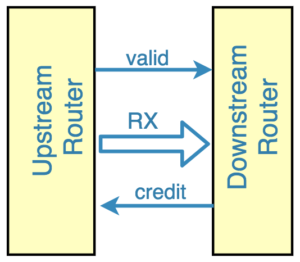

The routers flow control was replaced with a credit based flow control where the upstream router keeps track of the number of empty FIFO buffers in the downstream router in a counter (called credit counter). Once the upstream router sends a flit, it decreases this counter and once the downstream router passes one flit, it issues a signal (called credit) which will increase the counter in the upstream router.

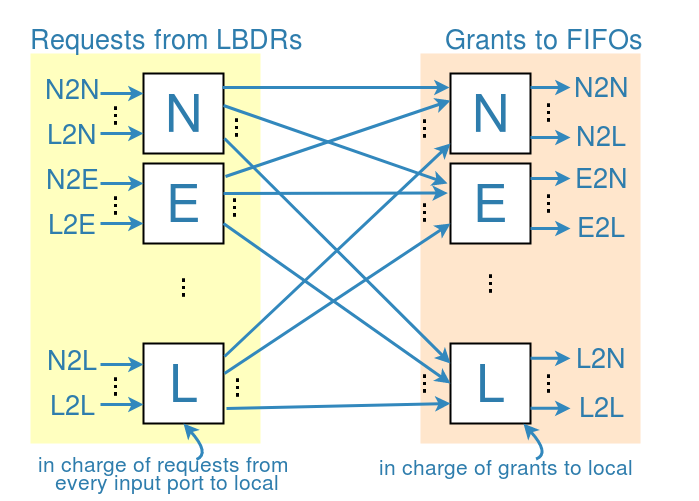

The set of arbiters were replaced with a two stage switch allocator unit. This will allow the router to handle multiple requests from a routing unit. I got the implementation details of this module from “Principles and Practices of Interconnection Networks”. Here is a simple block diagram:

This version of the router is maintained in the following github repository. There is a plan to clean this repo. But nobody has time for these stuff.

I will write about some dependability measures for this router in some future post.

—-

BTW, we have changed the packet format now. the old header flit is divided into 2 flits. the actual header flit is now only containing source and destination address and the 1st body flit is dedicated to holding packet id and packet length. This allows us to address up to 2^14 nodes. Which is absolutely amazing. Here is exactly how it looks:

Header: “001” & source_address (14 bits) & destination_address (14 bits) & parity bit

1st Body: “010” & packet_length (14 bits) & packet_id (14 bits) & parity bit

other Bodies: ” 010″ & payload (28 bits) & parity bit

Tail: ” 100″ & payload (28 bits) & parity bit